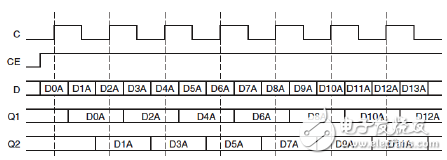

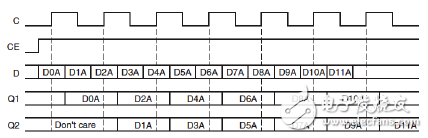

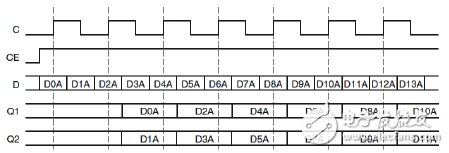

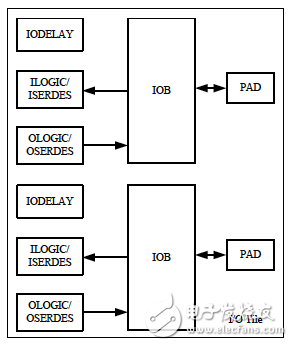

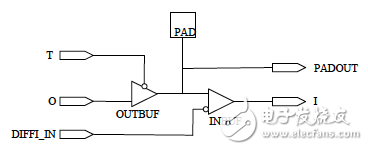

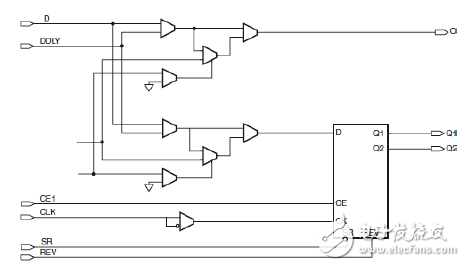

5.1.6 SelecTIO Module Each I/O slice (I/O TIle) of Virtex-6 contains two IOBs, two ILOGICs, two OLOGICs, and two IODELAYs, as shown in Figure 5-24. Figure 5-24 I/O slice structure This section introduces Virtex-6's SelecTIO resources in the following areas. (1) Electrical characteristics of SelecTIO. All Virtex-6 FPGAs feature high-performance configurable SelectIO drivers and receivers that support a wide range of interface standards. Powerful features SelectIO includes programmable control of output intensity and slope as well as on-chip termination using digitally controlled impedance (DCI). The IOB contains input, output, and tri-state SelectIO drivers. Single-ended I/O standards (LVCMOS, HSTL, SSTL) and differential I/O standards (LVDS, HT, LVPECL, BLVDS, differential HSTL, and SSTL) are supported. Note: The differential input and VREF related inputs are powered by VCCAUX. The connections for IOBs, pins, and internal logic are shown in Figure 5-25. Figure 5-25 IOB, pin and internal logic connection diagram The IOB is directly connected to the ILOGIC/OLOGIC pair, which contains input and output logic resources for data and tri-state control. ILOGIC and OLOGIC can be configured as ISERDES and OSERDES, respectively. The Xilinx software library provides a number of I/O-related primitives that can be specified when instantiating these primitives. Primitives related to single-ended I/O include IBUF (input buffer), IBUFG (clock input buffer), OBUF (output buffer), OBUFT (three-state output buffer), and IOBUF (input/output buffer) . Primitives related to differential I/O include IBUFDS (input buffer), IBUFGDS (clock input buffer), OBUFDS (output buffer), OBUFTDS (three-state output buffer), IOBUFDS (input/output buffer), IBUFDS_DIFF_OUT (input buffer) and IOBUFDS_DIFF_OUT (input/output buffer). SelectIO's logic resources mainly refer to ILOGIC and OLOGIC resources, which complete the FPGA pin to internal logic connection functions, including combined input / output, three-state output control, register input / output, register three-state output control, DDR input / Output, DDR output tri-state control, IODELAYE1 high-resolution adjustable delay unit and its control module. The following is a brief introduction to the ILOGIC and OLOGIC functions. (1) ILOGIC. Figure 5-26 ILOGIC internal logic The internal logic of ILOGIC is shown in Figure 5-26. The operations that can be implemented include: asynchronous/combination logic, DDR mode (OPPOSITE_EDGE, SAME_EDGE or SAME_EDGE_PIPELINED), level-sensitive latches and edge-triggered D-type flip-flops. Asynchronous/combination logic. Used to create a direct connection between the input driver and the internal resources of the FPGA. This path is automatically used when there is a direct (non-registered) connection between the input data and the FPGA internal logic, or when the "I/O registers/latch merges into the IOB" setting is OFF. Enter DDR (IDDR). Virgo-6 devices have dedicated registers in ILOGIC for input double data rate (DDR). This feature can be used by instantiating the primitives of IDDR. IDDR has only one clock input, and the falling edge data is clocked by the inverted version of the input clock (inverted in ILOGIC). The clocks of all input I/O modules are fully multiplexed, ie no clock is shared between ILOGIC or OLOGIC modules. IDDR supports the following three modes of operation: SAME_EDGE and SAME_EDGE_PIPELINED are the same as Virtex-5. These modes allow designers to transfer falling edge data to the rising edge clock domain within the ILOGIC module to save CLB and clock resources and improve performance. These modes are implemented using the DDR_CLK_EDGE attribute. Refer to Figure 5-27, Figure 5-28, and Figure 5-29 for the timing diagram for each mode. Figure 5-27 Input double data rate in OPPOSITE_EDGE mode Figure 5-28 Input double data rate in SAME_EDGE mode Figure 5-29 Input double data rate in SAME_EDGE_PIPELINED mode Programmable absolute delay unit IODELAYE1. Each I/O module contains a programmable absolute delay unit called IODELAYE1. IODELAYE1 can be connected to the ILOGIC/ISERDES or OLOGIC/OSERDES modules, or both. IODELAYE1 is a surround delay unit with 32 taps with a scaled tap resolution. Please refer to the Virtex-6 IO User Manual on the supplied CD-ROM. IODELAYE1 can be used to combine input channels, register input channels, combined output channels or registered output channels, and can be used directly in internal resources. IODELAYE1 allows for independent delay for each input signal. The tap delay resolution can be changed by selecting the IDELAYCTRL reference clock within the range specified in the Virtex-6 User Manual. The IODELAYE1 resource can be used as an IDELAY, ODELAY, or combined delay. .IDELAYE1 allows for independent delay for each input signal. The delay unit can be verified to an absolute delay value (TIDELAYRESOLUTION), which does not change with process, voltage and temperature changes. Enterprice energy efficiency management system is a complete set of solutions to provide enterprises with energy management,power quality and energy use safety monitoring.It includes the sources of energy(state grid,wind energy,photovoltaic power generation and other new energy sources,water,natural gas,fuel oil,etc.),the monitoring of energy use process,energy classification and sub-item energy consumption data statistics,and energy safety monitoring.This system is mainly used to help enterprises eliminate the blind area of energy consumption,improve the stability and security of energy supply system operation,and reduce the cost of operation and management for enterprises. electronic monitoring system ems,energy management system software,smart energy management system,energy data management system,energy management in buildings Jiangsu Acrel Electrical Manufacturing Co., LTD. , https://www.acrel.com.pk

(2) SelectIO's logical resources - ILOGIC resources and OLOGIC resources.

(3) SelectIO's advanced logic resources - ISERDES resources, OSERDES resources, and Bitslip.

OPPOSITE_EDGE mode, SAME_EDGE mode, and SAME_EDGE_PIPELINED mode.