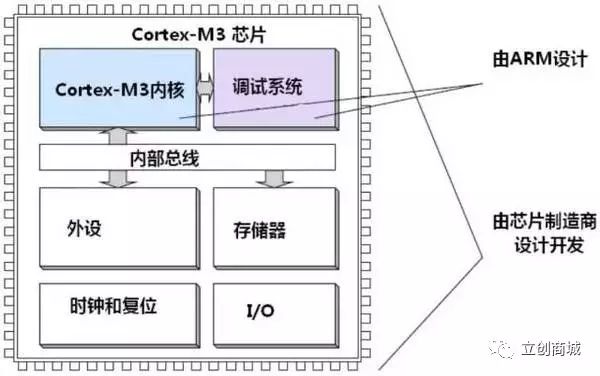

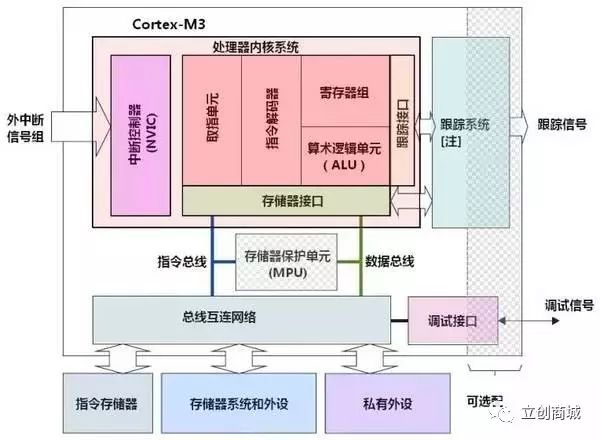

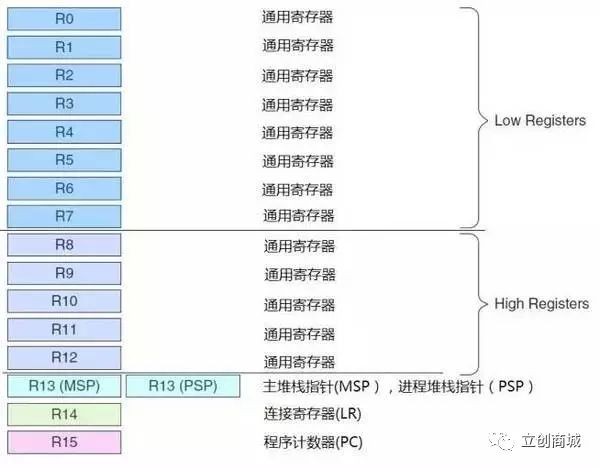

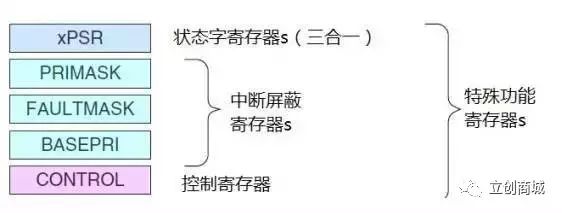

I. Abbreviations: AMBA: Advanced Microcontroller Bus Architecture ADK: AMBA Design Suite AHB: Advanced High Performance Bus AHB-AP: AHB Access Port APB: Advanced Peripheral Bus ARM ARM: ARM Architecture Reference Manual ASIC: Application-Specific Integrated Circuit ATB: Advanced Trace Bus BE8: Byte-Invariant Big Endian Mode CPI: Cycles Per Instruction DAP: Debug Access Port DSP: Digital Signal Processor DWT: Data Watchpoint and Trace ETM: Embedded Trace Macrocell FPB: Flash Patch and Breakpoint FSR: Fault Status Register HTM: CoreSight AHB Trace Macrocell ICE: In-Circuit Emulator IDE: Integrated Development Environment IRQ: Interrupt Request ISA: Instruction Set Architecture ISR: Interrupt Service Routine ITM: Instrumentation Trace Macrocell JTAG: Joint Test Action Group LR: Link Register LSB: Least Significant Bit MSB: Most Significant Bit LSU: Load/Store Unit MCU: Microcontroller Unit MPU: Memory Protection Unit MMU: Memory Management Unit MSP: Main Stack Pointer NMI: Non-Maskable Interrupt NVIC: Nested Vectored Interrupt Controller PC: Program Counter PPB: Private Peripheral Bus 2. Notations: 1. 4'hC, 0x123 represent hexadecimal numbers. 2. #3 refers to the number 3 (e.g., IRQ #3 means interrupt number 3). 3. #immed_12 represents a 12-bit immediate value. 4. Register bits usually denote a segment of a register. For example, Bit[15:12] indicates the bits from 15 down to 12. 3. Register Access Types: 1. R: Read-only 2. W: Write-only 3. RW: Read and write (common knowledge for most engineers) 4. R/Wc: Readable, but writing clears it to 0. Introduction to Cortex-M3 Chip 1. Basic Structure of the Chip: 2. ARMv7 Overview: In ARMv7, the architecture was divided into three different styles for the first time: Style A: Designed for high-performance "open application platforms" — closer to traditional computers. Style R: Targeted at high-end embedded systems with real-time requirements — fast and reliable. Style M: Designed for deeply embedded, microcontroller-style systems. 3. Stages of the Cortex-M3 Processor: The Cortex-M3 is ideal for applications that require high performance, code density, and minimal silicon area. It is widely used in: (1) Low-cost single-chip microcontrollers (2) Automotive electronics (3) Data communication systems (4) Industrial control systems (5) Consumer electronics 4. Overview of Cortex-M3: 1. Introduction: The Cortex-M3 is a 32-bit processor core with a 32-bit data path, 32-bit registers, and a 32-bit memory interface. It uses a Harvard architecture with separate instruction and data buses, allowing parallel access and improving performance. The internal bus interfaces are optimized for specific tasks and can operate in parallel, although both buses share the same memory space. The CM3 supports both little-endian and big-endian modes. It also provides an optional MPU and external cache for more complex applications. 2. Simplified Block Diagram: 3. Register Set: The Cortex-M3 has a set of registers R0-R15. R13 is the stack pointer (SP), which has two versions (MSP and PSP) that are banked and only one is active at a time. a. R0-R12 are general-purpose registers for data operations. Most 16-bit Thumb instructions can only access R0-R7, while 32-bit Thumb-2 instructions can access all registers. b. The main stack pointer (MSP) is used by the system and exception handlers, while the process stack pointer (PSP) is used by user applications. c. R14 (LR) stores the return address when calling a subroutine. d. R15 (PC) holds the current program counter address. Modifying it changes the execution flow. e. Special function registers include PSRs, PRIMASK, FAULTMASK, BASEPRI, and CONTROL. 4. Operating Modes and Privilege Levels: The Cortex-M3 supports two operating modes: thread mode and handler mode. Thread mode is used for normal application code, while handler mode is used for exception service routines. It also supports two privilege levels: privileged and unprivileged. This allows for secure memory access and protection against malicious or accidental modifications. By default, the processor starts in thread mode with privileged access. User-level programs must use system calls (like SVC) to switch back to privileged mode, ensuring controlled access to critical resources. 5. Nested Vectored Interrupt Controller (NVIC): The NVIC is tightly integrated with the Cortex-M3 core. It supports nested interrupts, vector interrupts, dynamic priority adjustment, and reduced interrupt latency. Vector interrupts allow the processor to automatically locate the correct interrupt service routine (ISR) based on the interrupt number, reducing latency and simplifying software development. 6. Memory Mapping: The Cortex-M3 supports a 4GB memory space, as shown in the following diagram: 7. Bus Interfaces: The Cortex-M3 includes multiple bus interfaces for simultaneous memory and peripheral access: - Instruction memory bus (two) - System bus - Private peripheral bus The I-Code and D-Code buses are used for code memory access, while the system bus handles memory and peripheral access. 8. Memory Protection Unit (MPU): The optional MPU provides memory protection by setting access permissions for privileged and unprivileged code. It generates fault exceptions when violations occur, helping to prevent corruption of critical data. The MPU is essential in safety-critical applications, such as aerospace, where system reliability is crucial. 9. Summary of Cortex-M3 Features: 1. High Performance: Many instructions execute in a single cycle. The separation of instruction and data buses improves efficiency. Thumb-2 instruction set reduces code size and increases code density. 2. Advanced Interrupt Handling: Integrated NVIC supports up to 240 external interrupts, with vectorized handling that reduces latency. Automatic context saving and restoring during interrupts speeds up response times. 3. Flexibility and Reliability: The Cortex-M3 is designed for high-frequency operation and offers features like NMI (non-maskable interrupt) and interrupt nesting for robust system behavior. Understanding these concepts lays the foundation for working with STM32 microcontrollers and other Cortex-M3-based systems. Liquid Cooling Motor For Construction Machinery liquid cooling motor for construction machinery Jiangsu Hengchi Motor Technology Co., Ltd , https://www.hcemotor.com

STM32 internal architecture and some classic design sharing

liquid cooling motor for construction machinery